### RESEARCH ARTICLE

**OPEN ACCESS**

# **Synthesis of Cordic Algorithm for Different Function**

## Ramanpreet Kaur\*, Parminder Singh Jassal\*\*

\* (M.Tech Student, Department of Electronics and Communication Engineering, Yadavindra College of Engineering, Punjabi University Guru kashi Campus, Talwandi Sabo – 151 302, Punjab (India) \*\*(Assistant Prof., Department of Electronics and Communication Engineering, Yadavindra College of Engineering, Punjabi University Guru kashi Campus, Talwandi Sabo – 151 302, Punjab (India))

#### Abstract

COordinate Rotation DIgital Computer (CORDIC) algorithm is very simple and iterative process for performing various mathematical computations. The development of CORDIC algorithm and architecture has taken place for achieving high throughput rate and reduction of hardware-complexity as well as the latency of implementation Most of the literature lacks in calculation of resources utilized by a particular CORDIC architecture. In this paper resource calculation and the design operation of various mathematical functions like divider, Rectangular to Polar conversion sin cos functions along with their accuracy is discussed.

Index Terms—CORDIC, Vector Rotation, Throughput

#### I. INTRODUCTION

CORDIC algorithm is an iterative algorithm, which can be used for the computation of trigonometric functions, multiplication and division [2]. Last half century has witnessed a lot of progress in design and development of architectures of the algorithm for high-performance and low-cost hardware solutions. CORDIC algorithm got its popularity, when [2] showed that, by varying a few simple parameters, it could be used as a single algorithm for unified implementation of a wide range of elementary transcendental functions involving logarithms, exponentials, and square. During the same time, [3] showed that CORDIC technique is a better choice for scientific calculator applications.

The popularity of CORDIC was very much enhanced thereafter primarily due to its potential for efficient and low-cost implementation. With the advent of low cost, low power FPGAs, this algorithm has shown its potential for efficient and low-cost implementation. CORDIC algorithm can be widely used in as wireless communications, Software Defined Radio and medical imaging applications, which are heavily dependent on signal processing.

Although CORDIC may not be the fastest technique to perform these operations, yet it is attractive due to the simplicity and efficient hardware implementation.

The development of CORDIC algorithm and architecture has taken place for achieving high throughput rate and reduction of hardware-complexity as well as the latency of implementation. Latency of implementation is an inherent drawback of the conventional CORDIC algorithm. Angle recoding schemes and higher radix CORDIC have been developed for reduced latency realization.

Parallel and pipelined CORDIC have been suggested high-throughput computation. computation is inherently sequential due to two main bottlenecks firstly the micro-rotation for any iteration is performed on the intermediate vector computed by the previous iteration and secondly the (i+1)th iteration could be started only after the completion of the ith iteration, since the value of which is required to start the (i+1)th iteration could be known only after the completion of the ith iteration. To alleviate the second bottleneck some attempts have been made for evaluation of values corresponding to small microrotation angles [5]. However, the CORDIC iterations could not still be performed in parallel due to the first bottleneck. A partial parallelization has been realized in [5] by combining a pair of conventional CORDIC iterations into a single merged iteration which provides better area-delay efficiency. But the accuracy is slightly affected by such merging and cannot be extended to a higher number of conventional CORDIC iterations since the induced error becomes unacceptable [4]. Parallel realization of CORDIC iterations to handle the first bottleneck by direct unfolding of micro-rotation is possible, but that would result in increase in computational complexity and the advantage of simplicity of CORDIC algorithm gets degraded [7]. Although no popular architectures are known to us for fully parallel implementation of CORDIC, different forms of pipelined implementation of CORDIC have however been proposed for improving computational throughput [8].To handle latency bottlenecks, various architectures have been developed and reported in this review. Most of the well-known architectures could be grouped under bit

www.ijera.com **99** | P a g e

parallel iterative CORDIC, bit parallel unrolled CORDIC, bit serial iterative CORDIC architecture.

### II. CORDIC ALGORITHM

Keeping the requirements and constraints of different application environments in view, the development of CORDIC algorithm and architecture has taken place for achieving high throughput rate and reduction of hardware-complexity as well as the latency of implementation. Some of the typical approaches for reduced-complexity implementation are focused on minimization of the complexity of scaling operation and the complexity of barrel-shifter in the CORDIC engine. Latency of implementation is an inherent drawback of the conventional CORDIC algorithm. Parallel and pipelined CORDIC have been suggested for high-throughput computation and efficient CORDIC algorithm.

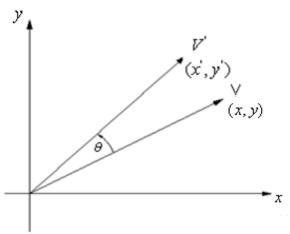

CORDIC algorithm has two types of computing modes Vector rotation (Rotating mode) and vector translation (Vectoring mode). The CORDIC algorithm was initially designed to perform a vector rotation, where the vector V with components (x,y) is rotated through the angle  $\theta$ yielding a new vector V' with component (x',y')shown in Fig 1.

Fig 1: Vector Rotation

$$V' = [R][V] \tag{1}$$

where R is the rotation matrix:

$$R = \begin{bmatrix} \cos \theta & -\sin \theta \\ \sin \theta & \cos \theta \end{bmatrix}$$

(2)

$$V' = \begin{bmatrix} x' \\ y' \end{bmatrix} = \begin{bmatrix} \cos \theta & -\sin \theta \\ \sin \theta & \cos \theta \end{bmatrix} \begin{bmatrix} x \\ y \end{bmatrix}$$

(3)

The individual equations for x and ybe rewritten as:

$x' = x \cdot \cos(\theta) - y \cdot \sin(\theta)$ (4)

$$y' = y.\cos(\theta) + x.\sin(\theta)$$

(5)

and rearranged so that

$$x' = \cos(\theta)[x - y.\tan(\theta)] \tag{6}$$

$$y' = \cos(\theta)[y + x.\tan(\theta)] \tag{7}$$

The multiplication by the tangent term can be avoided if the rotation angles and therefore  $tan(\theta)$  are restricted so that  $tan(\theta) = 2^{-i}$ . In digital hardware this denotes a simple shift operation. Furthermore, if those rotations are performed iteratively and in both directions every value of  $tan(\theta)$  is representable. With  $\theta = arctan(2^{-i})$  the cosine term could also be simplified and since  $cos(\theta) = cos(-\theta)$  it is a constant for a fixed number of iterations. This iterative rotation can now be expressed as:

$$x_{i+1} = k_i [x_i - y_i . d_i . 2^{-i}]$$

(8)

$$y_{i+1} = k_i [y_i + x_i . d_i . 2^{-i}]$$

(9)

where  $k_i = \cos(\arctan(2^{-i}))$  and  $d_i = \pm 1$ . The

product of the  $k_i$ 's represents the so-called K factor.

$$k = \prod_{i=0}^{n-1} k_i \tag{10}$$

This K factor can be calculated in advance and applied elsewhere in the system. Equations (8) and (9) can now be simplified to the basic CORDIC equations:

$$x_{i+1} = [x_i - y_i . d_i . 2^{-i}]$$

(11)

$$y_{i+1} = [y_i + x_i . d_i . 2^{-i}]$$

(12)

The direction of each rotation is defined by  $d_i$  and the sequence of all  $d_i$ 's determines the final vector. Each vector V can be described by either the vector length and angle or by its coordinates x and y. Following this incident, the CORDIC algorithm knows two ways of determining the direction of rotation: the rotation mode and the vectoring mode. Both methods initialize the angle accumulator with the desired angle  $z_o$ . The rotation mode, determines the right sequence as the angle accumulator approaches 0 while the vectoring mode minimizes the y component of the input vector.

The angle accumulator is defined by:

$$z_{i+1} = z_i - d_i. \arctan(2^{-i})$$

(13)

where the sum of an infinite number of iterative rotation angles equals the input angle  $\theta$ :

$$\theta = \sum_{i=0}^{\infty} d_i . \arctan(2^{-i})$$

(14)

www.ijera.com 100 | Page Those values of  $\arctan(2^{-i})$  can be stored in a small lookup table or hardwired depending on the way of implementation. Since the decision is which direction to rotate instead of whether to rotate or not,  $d_i$  is sensitive to the sign of  $z_i$ . Therefore  $d_i$  can be described as:

$$d_i = \begin{cases} -1, & \text{if} \quad z_i < 0 \\ +1, & \text{if} \quad z_i \ge 0 \end{cases}$$

(15)

With equation (15) the CORDIC algorithm in rotation mode is described completely. Note, that the CORDIC method as described performs rotations only within  $-\pi/2$  and  $\pi/2$ . This limitation comes from the use of  $2^0$  for the tangent in the first iteration. However, since a sine wave is symmetric from quadrant to quadrant, every sine value from 0 to  $2\pi$  can be represented by reflecting and/or inverting the first quadrant appropriately.

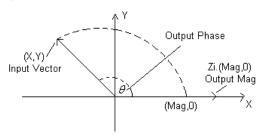

In vector translation, rotates the vector V with component (X, Y) around the circle until the Y component equals zero as illustrated in Figure 2. The outputs from vector translation are the magnitude X' and phase Z', of the input vector V with component (X,Y).

Fig 2. Vector Translation

After vector translation, output equations are:

$$X' = k_i \sqrt{\left(X^2 + Y^2\right)} \tag{16}$$

$$Y' = 0 \tag{17}$$

$$z' = a \tan\left(\frac{Y}{X}\right) \tag{18}$$

To achieve simplicity of hardware realization of the rotation, the key ideas used in CORDIC arithmetic are to decompose the rotations into a sequence of elementary rotations through predefined angles that could be implemented with minimum hardware cost and to avoid scaling, that might involve arithmetic operation, such as squareroot and division. The second idea is based on the fact the scale-factor contains only the magnitude

information but no information about the angle of rotation.

In 1971, John S. Walther found how CORDIC iterations could be modified to compute hyperbolic functions and reformulated the CORDIC algorithm into a generalized and unified form which is suitable to perform rotations in circular, hyperbolic and linear coordinate systems. The unified formulation includes a new variable m, which is assigned different values for different coordinate systems. The generalized CORDIC is formulated as follows:

$$x_{i+1} = x_i - m\sigma_i \cdot 2^{-i} \cdot y_i$$

$$y_{i+1} = y_i + \sigma_i \cdot 2^{-i} \cdot x_i$$

$$w_{i+1} = w_i - \sigma_i \cdot \alpha_i$$

(19)

Where

$$\sigma_i = \begin{cases} sign(w_i) & \text{for rotation mode} \\ -sign(w_i) & \text{for vectoring mode} \end{cases}$$

**Table 1 Generalized CORDIC Algorithm**

|    |                                            | 0                                   |

|----|--------------------------------------------|-------------------------------------|

| m  | Rotation mode                              | Vectoring mode                      |

|    | $x_n = k(x_o \cos w_o - y_o \sin w_o)$     | $x_n = k\sqrt{x_o^2 + y_o^2}$       |

| 0  | $y_n = k(x_o \sin w_o + y_o \cos w_o)$     | $y_n = 0$                           |

|    | $W_n = 0$                                  | $w_n = w_0 + \tan^{-1}(y_o/x_0)$    |

|    | $x_n = x_o$                                | $X_{\eta} = X_{\mathcal{O}}$        |

| 1  | $y_n = y_o + x_o w_o$                      | $y_n = 0$                           |

|    | $W_n = 0$                                  | $w_n = w_0 + (y_o / x_0)$           |

|    | $x_n = k_h(x_o \cosh w_o - y_o \sinh w_o)$ | $x_n = k_n \sqrt{x_o^2 + y_o^2}$    |

| -1 | $y_n = k_h(x_o \sinh w_o + y_o \cosh w_o)$ | $y_n = 0$                           |

|    | $w_n = 0$                                  | $w_n = w_0 + \tanh^{-1}(y_o / x_0)$ |

For m=1,0 or -1 and  $\alpha_i = \tan^{-1}(2^{-i}), 2^{-i}$  or  $\tanh^{-1}(2^{-i})$ , the algorithm given by (19) works in circular, linear or hyperbolic coordinate systems, respectively.

Table 1 summarizes the operations that can be performed in rotation and vectoring modes in each of these coordinate systems. The convergence range of linear and hyperbolic CORDIC are obtained, as in the case of circular coordinate, by the sum of all  $\alpha_i$  given by  $\sum_{i=0}^{\infty} \sigma_i$ .

The hyperbolic CORDIC requires to execute iterations for i=4,13,40... twice to ensure convergence. Consequently, these repetitions must be considered while computing the scale-factor  $K_h = \prod (1+2^{-2i})^{-1/2}$ , which converges to 0.8281.

www.ijera.com

### III. SYNTHESIS OF CORDIC ALGORITHM FOR RECTANGULAR TO POLAR CONVERSION

A logical extension to the sine and cosine computer is a polar to Cartesian coordinate transformer. The transformation from polar to Cartesian space is defined by

$$x = r \cos \theta$$

$y = r \sin \theta$

As pointed out above, the multiplication by the magnitude comes for free using the CORDIC rotator. The transformation is accomplished by selecting the rotation mode with  $x_0$ =polar magnitude,  $z_0$  = polar phase and  $y_0$ =0

Table 2 Resource Utilization of rectangular to polar conversion functional Configuration

| point conversion runteronal configuration            |      |           |  |

|------------------------------------------------------|------|-----------|--|

| Logic Utilization                                    | Used | Available |  |

| Number of Slice Flip Flops                           | 554  | 66,560    |  |

| Number of 4 input LUTs                               | 487  | 66,560    |  |

| Number of occupied Slices                            | 341  | 33,280    |  |

| Number of Slices<br>containing only related<br>logic | 341  | 341       |  |

| Total Number of 4 input LUTs                         | 562  | 66,560    |  |

| Number of MULT18X18s                                 | 81   | 104       |  |

| Number of GCLKs                                      | 1    | 8         |  |

Table 2 shows the logic resources used to implement the whole rectangular to polar architecture and its utilization.

### IV. SYNTHEISS OF CORDIC ALGORITHM FOR DIVIDER FUNCTIONS

The HDL integer divison operation is commonly supported in current development system for simulation . the divison algorithm are for simulation but difficult to synthesize. And is commonly used for hand written divison performed for binary numbers . The development system contain usually blocks for IP core generations where divison is solved in the form of highly pipelined synchronized cores that are able to work at high clock frequencies. The divider itself is a combinational block here is the resource calculation for the divider function of CORDIC.

Table 3 Resource Utilization of rectangular to polar conversion functional Configuration

| point conversion runctional configuration |      |           |  |

|-------------------------------------------|------|-----------|--|

| Logic Utilization                         | Used | Available |  |

| Number of Slice Flip Flops                | 1113 | 66,560    |  |

| Number of 4 input LUTs                    | 962  | 66,560    |  |

| Number of occupied Slices      | 745  | 33,280 |

|--------------------------------|------|--------|

| Number used as a route-through | 54   | 341    |

| Total Number of 4 input LUTs   | 1022 | 66,560 |

| Number of MULT18X18s           | 1    | 104    |

| Number of GCLKs                | 1    | 8      |

Table 3 shows the logic resources used to implement the whole Divider architecture and utilization of design is very less.

### V. V.SYNTHEISS OF CORDIC ALGORITHM FOR SIN AND COS FUNCTIONS

CORDIC can be used to compute Sin of any angle  $\theta$  with little variation. The angle is given as input. A vector length 1.647 (CORDIC gain) along the x-axis is taken. The vector is then rotated in steps so as to reach the desired input angle  $\theta$ . The x and y values are accumulated. After fixed number of iterations the final co-ordinates of the vector i.e. the x and y values give value of Cos and Sin respectively of the given angle  $\theta$ . When the Sin Cos functional configuration is selected, the unit vector is rotated, using the CORDIC algorithm, by input angle  $\theta$ . This generates the output vector  $(\cos(\theta), \sin(\theta))$ . The compensation scaling module is disabled for the Sin and Cos functional configuration as it is internally pre-scaled to compensate for the CORDIC scale factor.

**Table 4 Device Utilization Summary of Xilinx**

| Table 4 Device Utilization Summary of Amnix |      |            |           |

|---------------------------------------------|------|------------|-----------|

| Logic                                       | Used | Available  | Reference |

| Utilization                                 | OBCC | TTVUITUOTO | By [1]    |

| Number of                                   |      |            | 808       |

| occupied                                    | 277  | 33,280     |           |

| Slices                                      |      |            |           |

| Total Number                                |      |            | 1569      |

| of 4 input                                  | 507  | 66,560     |           |

| LUTs                                        |      |            |           |

| Number of 4                                 | 482  | 66,560     |           |

| input LUTs                                  | 462  | 00,500     |           |

| Number of                                   |      |            | 284       |

| Slice Flip                                  | 437  | 66,560     |           |

| Flops                                       |      |            |           |

| Number of                                   | 1    | 8          | 1         |

| GCLKs                                       | 1    |            |           |

Table 4 shows the logic resources used to implement the whole sin and cos architecture and utilization of design is less. Furthermore it is also shows the results of the reference paper [1].

www.ijera.com 102 | P a g e

Table 5 The Results of the Implementation of a Cordic Algorithm On Device and Matlab

| Angle  | Cos (Device) | Sin (Device) |

|--------|--------------|--------------|

| 61.25  | 0.4767       | 0.879        |

| 146.60 | -0.8311      | 0.5611       |

| 178.18 | -0.9917      | 0.1306       |

| Angle  | Cos (Matlab) | Sin (Matlab) |

|--------|--------------|--------------|

| 61.25  | 0.4738       | 0.8806       |

| 146.60 | -0.8278      | 0.5611       |

| 178.18 | -0.992       | 0.1266       |

Table 5 shows the results of the implementation of a cordic Algorithm on the device and Matlab and high process accuracy is obtained.

Table 6 Thermal Summary of sin cos functional

Configuration

| Thermal Summary    |       |  |

|--------------------|-------|--|

| Estimated Junction | 30C   |  |

| Temperature        | 300   |  |

| Ambient Temp       | 25C   |  |

| Case Temp          | 29C   |  |

| Theta J-A Range    | 13C/W |  |

Table 7 Results of error variance

| Cos       |           | Sin      |           |

|-----------|-----------|----------|-----------|

| Our work  | Ву        | Our work | Ву        |

|           | reference |          | reference |

|           | [1]       |          | [1]       |

| 7.19687e- | 8.6057e-  | 1.1103e- | 2.0431e-  |

| 006       | 005       | 005      | 004       |

According to the results of the above table 7, the accuracy of the result is verified as the error in cos and sin function is very negligible.

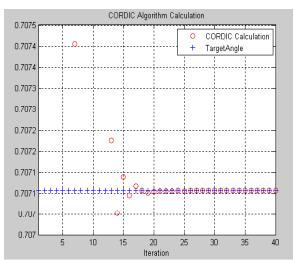

Fig 3. Effect of Iteration

Fig 3 shows the effect of iterations with the angle . as we increase the number of iterations ,more accurate results will be obtained.

#### VI. CONCLUSION

The Xilinx (ISE 9.2i) has been used to implement CORDIC functions as well as calculate the resource utilization. We have also compared our work with the results of the reference paper [1] and in our work the utilization of resources is less than the reference paper[1]. Furthermore the error variance is much negligible in our work. It means one can select a smaller and cheaper design to further reduce the cost as the Resource Utilization is reduced to large extent. Thermal summary for the mentioned functions has also been discussed.

#### REFERENCES

- [1] Buruc KIR Mehmet Ali ALTUCN, Suhap SAHIN, "FPGA Based Implementation of CORDIC using different number format" IEEE, 2013.

- [2] J. E. Volder, "The CORDIC trigonometric computing technique," IRE Transactions on Electronic Computers, vol. EC- 8, pp. 330–334, Sept. 1959.

- [3] J. S. Walther, "A unified algorithm for elementary functions," in Proceedings of the 38th Spring Joint Computer Conference, Atlantic City, NJ, 1971, pp.379–385.

- [4] D. S. Cochran, "Algorithms and accuracy in the HP-35," Hewlett-Packard Journal, pp. 1–11, June 1972.

- [5] S. Wang, V. Piuri, and J. E. E. Swartzlander, "Hybrid CORDIC algorithms," IEEE Transactions on Computers, volume 46, no. 11, pp. 1202–1207, November 1997.

- [6] S. Wang and E. E. Swartzlander, "Merged CORDIC algorithm," in IEEE International Symposium on Circuits Systems (ISCAS'95),1995, volume 3, pp.1988–1991.

- [7] B. Gisuthan and T. Srikanthan, "Pipelining flat CORDIC based trigonometric function generators," Microelectronics Journal, volume 33, Pp.77–89, 2002.

- [8] E. Deprettere, P. Dewilde, and R. Udo, "Pipelined CORDIC architectures for fast VLSI filtering and array processing," in IEEE International Conference on Acoustic, Speech, Signal Processing, ICASSP'84, March 1984, volume 9, pp.250–253.

- [9] D. E. Metafas and C. E. Goutis, "A floating point pipeline CORDIC processor with extended operation set," in IEEE International Symposium on Circuits and Systems, ISCAS'91, June 1991, volume 5, pp. 3066–3069.

www.ijera.com 103 | P a g e

Ramanpreet Kaur currently pursiving M-Tech degree in "Electronics & Communication Engineering" at Department of E&CE Yadavindra Collegeof Engineering, Talwandi Sabo. Her research interests are in simulation of digital circuits and FPGA Implementation.

Er. Parminder Singh Jassal received the M. Tech degree in VLSI Design from (C-DAC, Mohali) Punjab Technical University in 2006. He is currently working as Assistant Professor in Department of Electronics and Communication Engineering at Yadavindra College of Engineering, Punjabi University Guru kashi Campus, Talwandi Sabo. Previously working at NIT Hamirpur as a VLSI faculty under special Manpower development in VLSI Area (SMDP-II). His main research interests are in High speed digital VLSI circuits, Low power, synthesis and Simulation of digital circuits and FPGA Implementation.

www.ijera.com 104 | P a g e